반응형

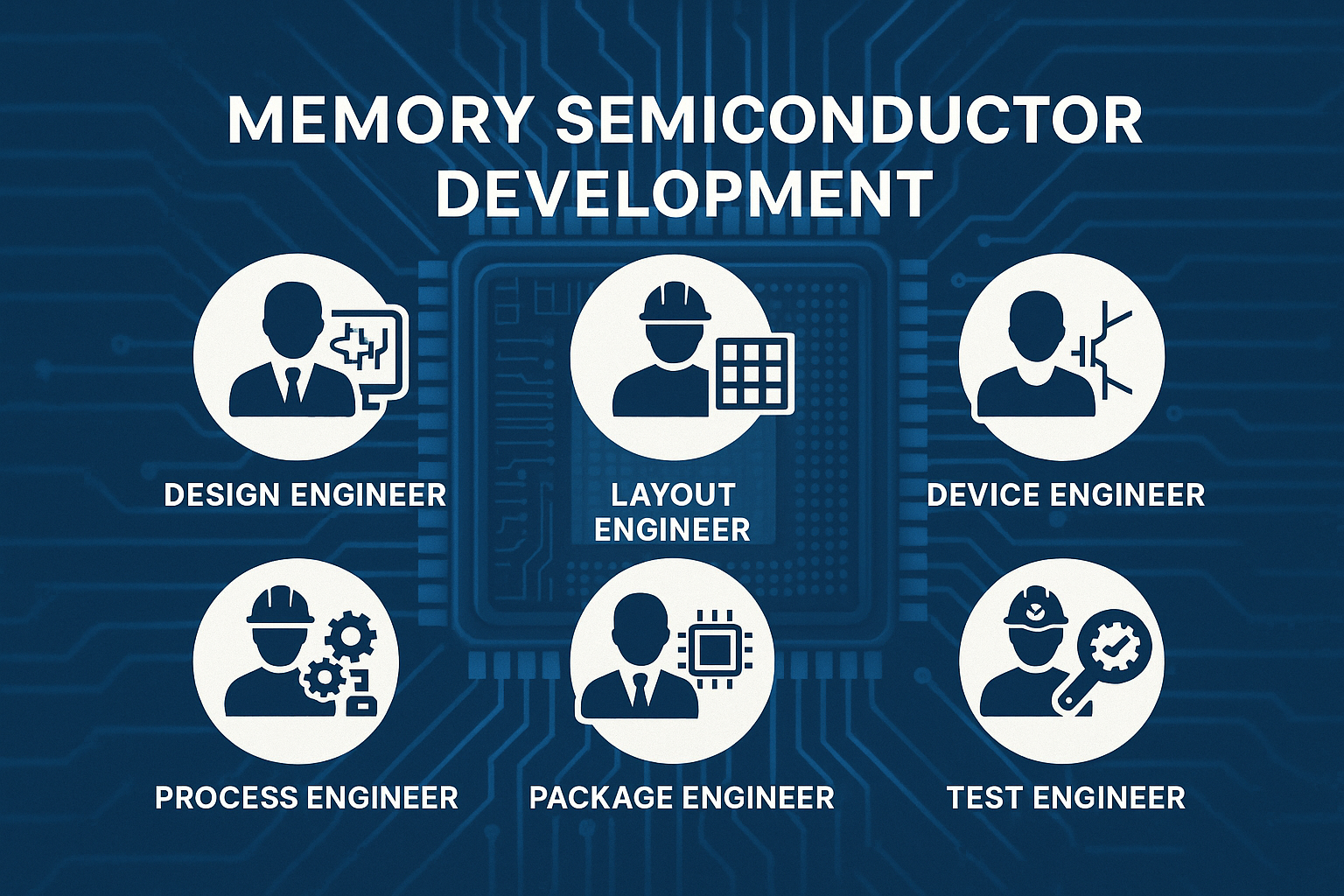

메모리 반도체 개발과정 A to Z: 각 직군별 역할 완전 정복

메모리 반도체(DRAM, NAND 등)는 현대 전자기기의 핵심 부품입니다. 스마트폰, 노트북, 서버, 전기차에 이르기까지 다양한 제품에 사용되며, 그 개발 과정은 수많은 전문 엔지니어의 협업으로 이루어집니다. 이 글에서는 메모리 반도체가 기획부터 테스트까지 어떻게 개발되는지 각 직군의 역할을 중심으로 구체적으로 설명드립니다.

1. 메모리 반도체 개발 주요 단계

메모리 반도체는 단순히 하나의 설계나 공정으로 끝나는 것이 아니라, 수많은 과정을 거쳐 최종 제품으로 완성됩니다. 개발 흐름은 다음과 같은 6단계로 나뉘며, 각 단계에는 전문 직군이 핵심적으로 투입되어 완성도를 높입니다.

- 제품 기획 및 사양 정의: 시장의 니즈와 고객 요구사항을 바탕으로 제품의 사양을 결정하는 단계입니다. 어떤 용량의 메모리인지, 어떤 속도와 전력 특성을 가질지 정의되며, 이 때부터 전체 개발 방향이 정해집니다.

- 회로 및 소자 설계: 제품 사양에 맞는 회로 구조와 메모리 셀을 설계합니다. 회로 설계는 데이터 입출력 흐름과 전원 분배 등을 고려하고, 소자 설계는 트랜지스터와 캐패시터 구조를 최적화하여 셀 성능을 높입니다.

- 레이아웃 설계: 실제 반도체 칩 위에 회로가 배치되는 단계입니다. 레이아웃 엔지니어는 회로 설계 정보를 기반으로 트랜지스터와 배선을 2D 평면에 설계하고, 공정 가능성과 성능을 함께 고려합니다.

- 공정 개발 및 양산 준비: 반도체 제조에 필요한 모든 공정 조건을 설정하고, 공정별 변수들을 최적화합니다. 각 공정이 정밀하게 제어되어야 수율과 품질이 확보됩니다.

- 패키징 설계 및 조립: 제조된 칩을 외부 환경으로부터 보호하고, 시스템 보드와의 연결을 가능하게 하는 패키지를 설계합니다. 기계적 안정성, 열 해소, 전기적 연결성을 종합적으로 고려합니다.

- 테스트 및 품질 평가: 모든 과정을 거친 반도체 칩의 기능과 신뢰성을 평가합니다. 자동화 테스트 장비를 활용하여 불량을 검출하고, 수율을 분석하며, 개선사항을 도출합니다.

2. 직군별 상세 역할 및 업무 프로세스

2.1 설계 엔지니어 (Circuit Design Engineer)

- 제품 스펙 정의: 시장 요구, 고객 요청, 경쟁사 제품을 분석해 용량, 속도, 전력 소비 등의 제품 사양을 정리합니다.

- 회로 설계: DRAM 셀 어레이, 리프레시 회로, I/O 회로, 타이밍 회로 등 다양한 구성요소를 설계합니다.

- 시뮬레이션: SPICE, Verilog 등을 이용한 전기적 시뮬레이션을 통해 타이밍과 기능을 검증합니다.

- 설계 자동화: 설계 시간 단축과 오류 방지를 위한 자동화 스크립트 및 IP 재사용 구조 설계

- 후반 피드백: 테스트에서 발견된 불량에 대해 회로적 관점에서 원인을 분석하고 개선 설계안을 제시합니다.

2.2 소자 엔지니어 (Device Engineer)

- 셀 구조 설계: 고집적, 고속, 저전력 셀 구조(예: 4F2 구조)를 연구하고 설계합니다.

- 소자 모델링: 트랜지스터, 캐패시터의 특성 곡선을 시뮬레이션하고 SPICE 모델을 구축합니다.

- 전기적 특성 평가: E-test, IV/CV, BTI/PBTI 측정을 통해 실제 웨이퍼 특성을 평가하고 스펙에 맞게 튜닝합니다.

- Design Rule 제정: 회로 설계 및 레이아웃 팀이 사용할 수 있는 소자 기준치를 문서화합니다.

- 신소자 개발: 차세대 DRAM(1a, 1z), 3D-NAND용 소재 및 구조 연구 수행

2.3 레이아웃 엔지니어 (Layout Engineer)

- 회로 배치: 설계자가 만든 회로도를 기반으로 트랜지스터, 메탈 배선 등을 물리적으로 배치합니다.

- Design Rule Check(DRC): 공정 규칙에 맞는 설계 여부를 자동화 툴로 검증합니다.

- LVS (Layout vs Schematic): 회로도와 물리적 레이아웃 간 불일치 여부를 검증합니다.

- 면적 최적화: 다이 크기를 최소화하고 성능을 최대로 끌어올리는 물리적 설계를 수행합니다.

- 층간 배선 최적화: multi-metal layer를 고려한 최적 라우팅 설계

2.4 공정 엔지니어 (Process Engineer)

- 공정 조건 설정: 포토(노광), 식각, 증착, 이온주입, CMP 등 8대 공정에 맞는 레시피 설정

- Defect 분석: 수율 저하의 원인을 데이터 기반으로 분석하고 개선안을 제시합니다.

- Inline 모니터링: 실시간 센서와 데이터 분석으로 공정 이상을 감지하고 대응합니다.

- 신공정 개발: 차세대 소재(SiGe, HKMG 등)와 공정 기법(Spacer Patterning 등) 적용 검토 및 개발

- 양산 전이: Lab 공정 → Pilot Line → 양산 Fab 이전을 위한 조건 검증 및 표준화

2.5 패키지 엔지니어 (Package Engineer)

- 패키지 설계: WLP, BGA, PoP 등 메모리 제품의 특성에 적합한 패키지 구조 설계

- 배선 설계: 칩 내부 패드와 외부 단자 간 전기 신호를 위한 배선 최적화

- 열/기계 해석: FEA, CFD를 통한 구조적 안정성 확보

- 재료 선택: EM/TSV/Substrate 등 신소재 적용 및 검증

- 조립성 검토: 제조 현장(FATP)과의 연계 및 조립 공정성 확인

2.6 테스트 엔지니어 (Test Engineer)

- 테스트 벡터 개발: 기능 검사, 타이밍 검사, 전력 검사에 필요한 패턴 생성

- ATE 운영: Advantest, Teradyne 등의 자동 테스트 장비 셋업 및 실행

- 수율 분석: Bin 분석, Wafer Map 분석 등을 통해 양품/불량 원인을 분석합니다.

- 신뢰성 테스트: HTOL, TDBI, AC/DC 전압 스트레스 등으로 장기 신뢰성 확인

- 피드백 제공: 불량 원인별로 설계/공정/패키지 부서에 개선 요청

3. 결론: 정밀한 협업의 산물

반도체는 단일한 직무의 산물이 아닙니다. 회로를 상상하는 사람, 소자를 구현하는 사람, 그걸 실제로 만들고 평가하고 포장하고 검사하는 사람들이 정밀하게 맞물릴 때 비로소 하나의 반도체가 탄생합니다. 메모리 반도체 개발은 바로 그런 협업의 결정체입니다.

📚 함께 읽으면 좋은 글

반응형

'데이빗의 반도체 이야기' 카테고리의 다른 글

| 반도체 회사의 워라밸과 성과, 결국 개인의 선택.. (1) | 2025.06.17 |

|---|---|

| 반도체 회사 합격 전략과 준비 사항, 지원자를 위한 구체적 조언 (4) | 2025.06.16 |

| 반도체 PI 직무란? 공정 통합 전문가의 역할과 단위 공정 엔지니어와의 차이 (1) | 2025.06.13 |

| CXL 이란? CXL 의 뜻과 장점, 그리고 리스크에 대해 알아보기. (52) | 2024.04.16 |

| 반도체 엔지니어가 알려주는 PI 직무 (0) | 2023.10.10 |